지난 시기 여러 형태의 자료들을 받아 콤퓨터로 전송하는 자료수집체계들에 대한 연구들이 진행되여 현장대상조종이나 화상처리, 음성처리 등에 리용되였다. 이러한 자료수집체계들에서는 수신대면부로서 PCI를 리용하였으며 수신된 자료는 현시기에 전송하든가 펌웨어작성을 필요로 하지 않는 USB대면부를 리용하였다. 또한 SDRAM을 리용하는 경우 반드시 제기되는 SDRAM조종기의 실현에서 FPGA자원소비가 많아지고 우리의 요구에 맞는 동작특성을 기대하기 어렵게 되였다.

우리는 LVDS대면부를 리용하여 자료를 고속으로 수신 및 저장하고 저장자료를 USB2.0의 고속자료전송방식으로 콤퓨터에 전송하는 LVDS-USB변환체계를 실현하기 위하여 먼저 FPGA를 리용하여 SDRAM조종기설계를 한개의 FSM으로 SDRAM에 대한 읽기 및 쓰기를 진행할수 있도록 설계하였다.

또한 SDRAM으로부터의 자료는 EZ-USB의 GPIF에 의해 USB포구로 전송된다. 이때 24bit자료를 16bit자료로 변환하는 기능을 수행하는 자료변환기의 모형을 설계하였다.

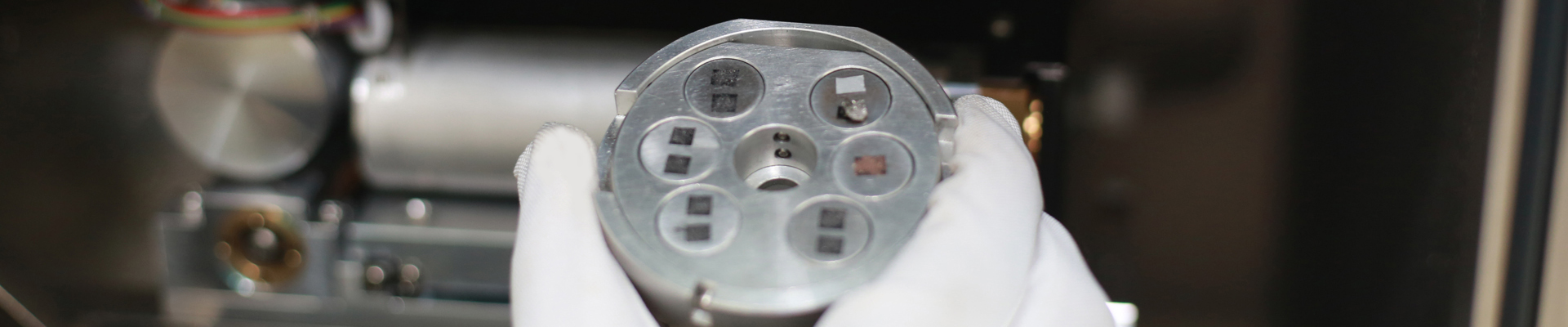

이에 기초하여 자료저장기와 자료변환기모형을 Verilog HDL로 서술하여 Cyclone III FPGA로 실현하였으며 EZ-USB전송체계를 실현하기 위한 EZ-USB펌웨어설계와 상위프로그람설계를 진행하였다.

실험결과 SDRAM의 동작주파수가 133MHz일 때 16M×32bit의 자료를 저장하는데 걸리는 시간은 1.2s이며 설계한 자료저장조종기는 보다 적은 FPGA자원을 소모하면서도 전송속도가 80MByte/s인 LVDS대면부로부터의 자료를 저장한다는것을 확증하였다.

이상의 연구결과는 잡지 «Информационные технологии Проблемы и решения»에 《A study on the implementation of LVDS-USB conversion system using FPGA》(https://elibrary.ru/title_about.asp)의 제목으로 출판되였다.